Synopsys Demos PCIe 5.0 IP Interoperability With Intel Future Xeon Scalable Processor

Enables low-risk integration and adoption of PCIe 5.0 interface in HPC SoCs.

This is a Press Release edited by StorageNewsletter.com on October 19, 2020 at 2:24 pmSynopsys, Inc. announced its collaboration with Intel Corp. to achieve system-level interoperability between the DesignWare Controller and PHY IP for PCIe 5.0 and future Xeon Scalable processors (codenamed Sapphire Rapids).

The full-system interoperability, a milestone in the firm and Intel’s ongoing collaboration, enables the ecosystem to confidently use the companies’ proven technologies to accelerate development of their PCIe 5.0-based products in HPC and AI applications. The DesignWare IP for PCIe 5.0 has been licensed over a hundred times by customers across all key market segments, delivering the lowest latency and highest throughput IP compared to other solutions.

“Synopsys continues to collaborate with industry leaders like Intel to deliver high-quality IP that help designers address the bandwidth, power, area, and latency demands for the new era of high-performance computing systems,” said John Koeter, SVP, marketing and strategy, IP. “Achieving successful interoperability between Synopsys’ DesignWare IP for PCIe 5.0 and Intel Xeon Scalable processors validates that the IP functions as intended with Intel’s industry-standard PCIe 5.0 products, accelerating the path to first-silicon success with less risk.“

“The growth of high-performance computing applications converged with AI workloads requires innovative data connectivity and processing technologies that deliver low latency and fast speeds,” said Jim Pappas, director, technology initiatives, Intel. “We are pleased to collaborate with Synopsys, a leading provider of PCIe IP, to enable the ecosystem and ensure the widely adopted DesignWare IP for PCIe 5.0 is interoperable with our future CPUs in order to enable the billions of PCIe-enabled products in the market.“

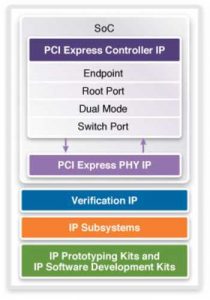

The DesignWare Controller, PHY, and Verification IP for PCIe 5.0 in a range of FinFET processes from 16nm to 5nm is available.

Video: What’s Hot in DesignWare PCIe 5.0 IP

Read also:

PCI-SIG DevCon Taiwan: Astera Labs Demos PCIe 5.0 System Deployment in Collaboration With Intel and Synopsys

With Smart Retimer 32GT/s retimer SoC designed to PCIe 5.0 spec, doubles signal reach and achieves plug-and-play interoperation without compromising interconnect topologies even at 32 GT/s speeds.

Ocober 28, 2019 | Press Release

Astera Labs Collaborates With Synopsys

To develop PCIe 5.0 connectivity for next-gen servers running on AWS

June 13, 2019 | Press Release

Synopsys: DDR5 NVDIMM-P Verification IP for Next-Gen Storage-Class Memory Designs

With fast integration and performance, resulting in accelerated verification closure

May 6, 2019 | Press Release

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter