ATP Electronics Extends 3D TLC NAND e.MMC Devices Endurance to MLC/SLC Levels

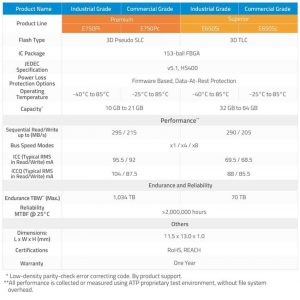

Comply with JEDEC e.MMC v5.1 standard, supporting fast 400 DDR mode for up to 400MB/s, E750Pi and E650Si Series operable at -40°C to 85°C, and E750Pc and E650Sc at -25°C to 85°C for applications with non-critical thermal requirements

This is a Press Release edited by StorageNewsletter.com on February 25, 2022 at 2:01 pmATP Electronics, Inc. has introduced its latest line of e.MMC devices built on 3D TLC NAND.

Using a new die package, the E750Pi/Pc and E650Si/Sc Series offer long-life performance, optimized power consumption and customizable configuration options.

The series e.MMC offerings are built with 3D TLC NAND flash but are configured as pseudo SLC (pSLC) to offer endurance on par with SLC NAND, while E650Si/Sc Series in native TLC has near-MLC endurance.

The E750Pi and E650Si Series are industrial temperature-operable (-40°C to 85°C), making them for deployment in scenarios with thermal challenges and harsh environments, while E750Pc and E650Sc support -25°C to 85°C operating temperatures for applications with non-critical thermal requirements.

“Industrial and embedded applications are becoming more varied, requiring storage devices to be more flexible with a wide array of specs and options. The ATP e.MMC’s small footprint makes it a suitable, cost-effective solution for space-constrained environments. As a soldered-down solution, it is shock/vibration proof, so it has become a preferred storage medium for extremely rugged operations.” said Chris Lien, head, embedded business unit. “As customers become more discerning in choosing storage solutions to meet specific needs, ATP’s customization capabilities allow us to tailor-fit configurations to deliver better power efficiency, space-saving packages, and ball variations.“

Huge features in tiny footprint

Consuming low power during Sleep Mode, the E750Pi/Pc and E650Si/Sc Series e.MMC deliver power savings. These e.MMC offerings comply with JEDEC e.MMC v5.1 standard (JESD84-B51), supporting high-speed 400 (HS400) DDR mode for a bandwidth of up to 400MB/s.

The E650Si/Sc Series in native TLC offer capacities from 32 to 64GB for use in mass storage applications, while the E750Pi/Pc in pSLC mode are available in capacities from 10GB to 21GB, which cuts down the TLC capacity but improves performance, reliability, and endurance.

Data integrity features

The E750Pi/Pc and E650Si/Sc Series e.MMC feature the following technologies to ensure data integrity:

-

AutoRefresh technology improves the data integrity of read-only areas by monitoring the error bit level and read counts in every read operation.

-

Dynamic data refresh technology reduces the risks of read disturb and sustains data integrity in seldom-accessed areas.

-

SRAM soft error detector and recovery mechanism maximizes data integrity by monitoring soft errors, which cannot be detected nor solved by ECC engines and can therefore jeopardize data accuracy.

-

Low-Density Parity-Check Error Correcting Code (LDPC ECC) provides error correction to improve data transfer reliability.

Customizable configurations

Apart from the standard e.MMC size of 11.5x13mm, customers may request a customized package size, such as the 9x10mm option, for up to 40% space savings. The company also offers value-added services to optimize and tune power consumption. The E750Pi/Pc and E650Si/Sc Series e.MMC come in the standard 153-ball grid array (BGA) but depending on project, other ball variations such as the 100-ball option, may be requested. Other customizable configurations include firmware, testing, laser markings, and other specific features to meet their investment and application requirements.

Click to enlarge

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter