Cadence Design IP Supporting PCIe 6.0 Spec on TSMC N5 Process

Consists of performance DSP-based PHY and feature companion controller to deliver optimized performance and throughput for next-gen applications in hyperscale computing and 5G communications, including networking, emerging memory and storage.

This is a Press Release edited by StorageNewsletter.com on October 27, 2021 at 2:01 pmCadence Design Systems, Inc. announced the availability of its IP supporting the PCIe 6.0 spec on the TSMC N5 process.

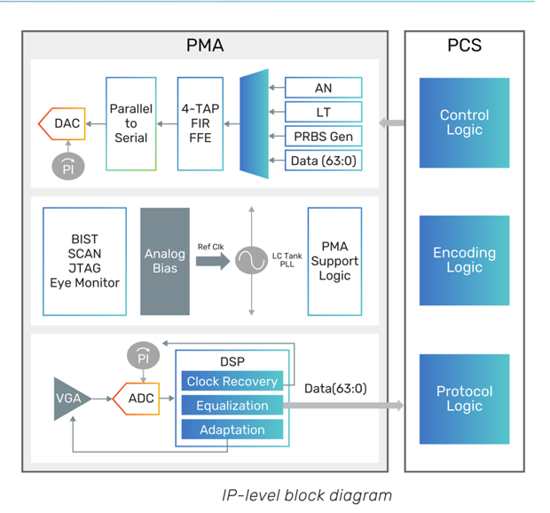

The IP for PCIe 6.0 consists of a performance DSP-based PHY and a feature-rich companion controller to deliver the performance and throughput for next-gen applications in hyperscale computing and 5G communications, including networking, emerging memory and storage. Early adopters of the company’s IP for PCIe 6.0 can access design kits now.

The 5nm PCIe 6.0 PHY test chip silicon demonstrated excellent electrical performance across all PCIe rates. The PAM4/NRZ dual-mode transmitter delivered optimal signal integrity, symmetry and linearity with low jitter. The DSP-based receiver demonstrated data recovery capabilities while withstanding harsh signal impairments and channel loss in excess of 35dB at 64GT/s. In addition, the DSP core in the PHY provides continuous background adaptation to monitor and compensate for the signal fluctuations induced by environmental factors, achieving enhanced reliability.

The controller IP for PCIe 6.0 is designed to provide the highest link throughput and utilization while operating with extremely low latency. The highly scalable multi-packet processing architecture supports up to 1,024-bit wide data path in x16 configuration while operating at 1GHz to achieve maximum aggregate bandwidth of 128Gb/s. The controller supports all the PCIe 6.0 features, including PAM4 signaling, Forward Error Correction (FEC), FLIT Encoding and L0p power state while retaining full backward compatibility.

A PCIe 6.0 subsystem test chip was taped out on TSMC N5 in July 2021. This subsystem test chip integrated the second-gen power, performance and area (PPA)-optimized PCIe 6.0 PHY together with the PCIe 6.0 controller. This subsystem test chip enables Cadence to validate PCIe 6.0 PHY and controller functions at the system level and perform rigorous compliance and stress tests to ensure universal interoperability and reliability.

“We work closely with Cadence, our long-standing ecosystem partner, to enable next-gen designs benefiting from the significant power, performance and area improvements of our advanced technologies,” said Suk Lee, VP, design infrastructure management division, TSMC (Taiwan Semiconductor Manufacturing Company). “This collaborative effort combining Cadence’s leading IP solution with TSMC’s 5nm technology will help our mutual customers meet the most challenging power and performance requirements and quickly launch their differentiated product innovations.“

“Early adopters have already started exploring with the new PCIe6 spec, and we are looking forward to seeing them achieve positive results with TSMC and Cadence technologies,” said Sanjive Agarwala, corporate VP and GM,IP group, Cadence. “We’ve been deploying PAM4-based IP since 2019 when we introduced our first-gen 112G-LR SerDes IP, and our vast expertise in PAM4 technology plus our strong collaboration with TSMC provides a robust foundation for success with our PCIe6 products.“

The company’s IP for the PCIe 6.0 spec supports the firm’s ‘Intelligent System Design’ strategy, which enables SoC design excellence. The company’s portfolio of design IP solutions for TSMC’s advanced processes also includes 112G, 56G, die-to-die (D2D) and advanced memory IP solutions.

Resource:

Cadence PCIe IP solution

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter