Availability of Arasan UFS 5.0 Host Controller IP

Available immediately for ASIC and FPGA applications

This is a Press Release edited by StorageNewsletter.com on May 5, 2026 at 2:00 pmArasan Chip Systems, Inc. extends its long history of support for JEDEC and MIPI standards with the immediate availability of UFS 5.0 host controller IP. The company’s UFS 5.0 host controller IP supports a maximum throughput of 46.694Gb/s with M-PHY HS-Gear 6 operation, providing very high data transfer rates with low power consumption for advanced mobile applications such as high end smartphone and edge AI devices.

The company’s UFS 5.0 host controller IP supports a maximum throughput of 46.694Gb/s with M-PHY HS-Gear 6 operation, providing very high data transfer rates with low power consumption for advanced mobile applications such as high end smartphone and edge AI devices.

The firm joined the UFS Association in 2010 and was the industry’s first provider of a Total UFS IP solutions along with the M-PHY IP in 2011. The company’s UFS IP has been licensed by major memory vendors and semiconductor companies since 2011. Its UFS IP is the de facto standard IP used in UFS production testers and UFS compliance testers.

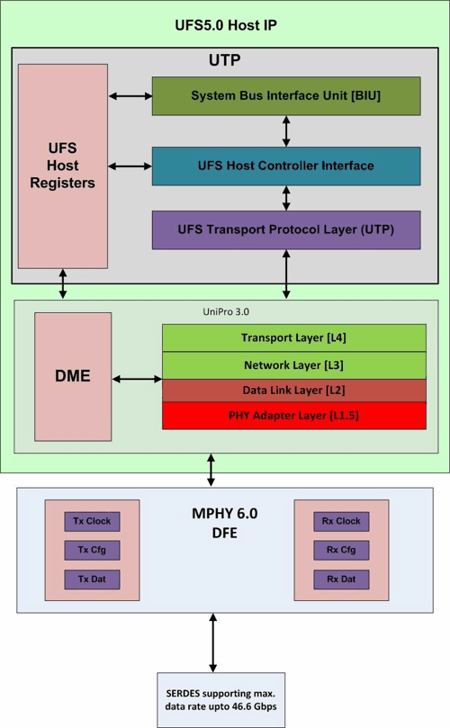

Arasan UFS 5.0 Host Controller IP Block Diagram

Universal Flash Storage (UFS) is a JEDEC standard for high performance mobile storage devices suitable for next-gen data storage. UFS is also adopted by Mobile Industry Processor Interface (MIPI) as a data transfer standard designed for mobile systems. UFS incorporates the MIPI UniPro standard as well as the MIPI Alliance M-PHY standard. Arasan has been an executive member of the MIPI Association since 2005 and provides the broadest portfolio of MIPI IP, including UNIPRO IP and M-PHY IP.

Universal Flash Storage (UFS) is a JEDEC standard for high performance mobile storage devices suitable for next-gen data storage. UFS is also adopted by Mobile Industry Processor Interface (MIPI) as a data transfer standard designed for mobile systems. UFS incorporates the MIPI UniPro standard as well as the MIPI Alliance M-PHY standard. Arasan has been an executive member of the MIPI Association since 2005 and provides the broadest portfolio of MIPI IP, including UNIPRO IP and M-PHY IP.

“We are proud to extend our leadership in UFS with the announcement of our UFS 5.0 Host IP. This IP addresses the need for higher speeds in mobile applications that require a high throughput with low power consumption and low pin count. We look forward to our compliant UFS 5.0 IP proven in production testers and emulation platforms accelerating UFS 5.0 adoption in ASIC’s” said Prakash Kamath, CTO, Arasan.

Arasan’s UFS 5.0 Host IP joins its complete portfolio of solid state memory IP solutions including xSPI IP and PSRAM IP for the NOR Flash, eMMC controller for low throughput NAND Flash applications and NAND Flash Controller IP with integrated PHY IP. The PHY IP are available in nodes down to 4nm on major foundries.

The company’s UFS 5.0 Host IP is available for immediate licensing along with the M-PHY DFE (Digital Front End) and UFS 5.0 Software Stack. Arasan UFS 5.0 Host IP is available for use on FPGA and ASIC applications.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter