FMS 2025: Chelsio Sampling T7 DPU Platform

Available in 2 ASIC variants: T7 full-featured DPU silicon for storage appliances, security platforms, and AI networking, and S7 cost-optimized, DRAM-less variant designed for high-volume cloud and server environments

This is a Press Release edited by StorageNewsletter.com on August 7, 2025 at 2:01 pmChelsio Communications, Inc. announced the broad sampling availability of its T7 Data Processing Unit (DPU).

After a year of early-access deployments with select customers in AI, storage, and cloud markets, the company is now making T7 silicon more broadly accessible. This release incorporates customer-driven enhancements and architectural innovations designed to meet the growing demand for Ethernet-based acceleration in high-performance infrastructure. Purpose-built for high-throughput, low-latency networking, the T7 enables line-rate offloads up to 400GbE, with comprehensive support for data security, integrity, and scalable storage design.

After a year of early-access deployments with select customers in AI, storage, and cloud markets, the company is now making T7 silicon more broadly accessible. This release incorporates customer-driven enhancements and architectural innovations designed to meet the growing demand for Ethernet-based acceleration in high-performance infrastructure. Purpose-built for high-throughput, low-latency networking, the T7 enables line-rate offloads up to 400GbE, with comprehensive support for data security, integrity, and scalable storage design.

“T7 is the first DPU-class solution from Chelsio, engineered from the ground up to handle modern offload requirements in AI, storage, and security environments,” said Kianoosh Naghshineh, CEO, Chelsio Communications. “This broader sampling release represents the maturity of our platform and the result of deep collaboration with early adopters who demanded open, efficient Ethernet-based solutions.”

- Full hardware offload for NVMe/TCP, NVMe-oF (iWARP and RoCEv2), UDP, and iSCSI, enabling ultra-low-latency JBOF and all-flash storage deployments

- In-line support for IPsec, TLS, kTLS, traffic filtering, and advanced packet classification to secure data-in-motion

- Controller Memory Buffer (CMB) and advanced NVMe features for latency-sensitive applications and low-overhead data movement

- Hardware-based end-to-end data integrity protection

- Sustained 400GbE line-rate offload across diverse storage, networking, and security workloads

- Integrated hardware engines for compression, deduplication, RSA, RAID 5/6, Erasure Coding, and PMoF (Persistent Memory over Fabrics) as well as QUIC. Drivers for these capabilities will be available soon.

- Built-in PCIe switch functionality for adapter or host mode

- Native FPGA integration interface for highly customizable acceleration

- Flexible architecture capable of hosting multiple adapters – or acting as a hosted endpoint by upstream CPUs

Platform Flexibility

The T7 DPU platform is available in 2 ASIC variants, optimized for different deployment needs:

-

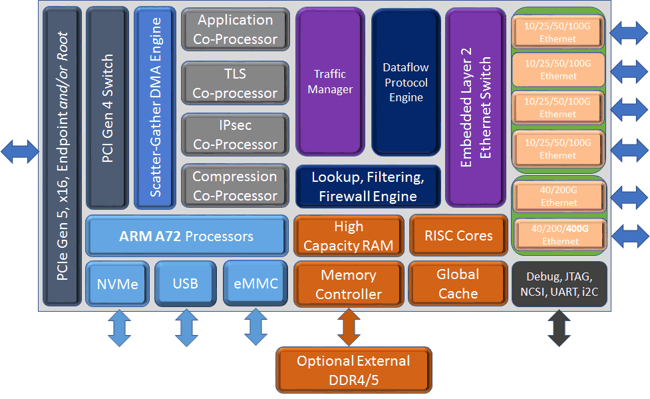

T7: Full-featured DPU silicon for storage appliances, security platforms, and AI networking

T7 diagram

-

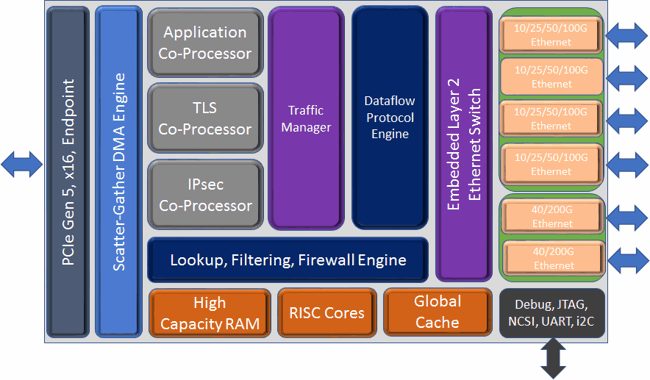

S7: A cost-optimized, DRAM-less variant designed for high-volume cloud and server environments, ideal for migrating hardware offloads from appliances to disaggregated cloud infrastructure

S7 diagram

The T7 platform introduces novel data paths to unify switch, FPGA, and compute functions, enabling purpose-built acceleration pipelines tailored to customer workloads. By offloading infrastructure tasks traditionally managed by general-purpose CPUs, the T7 paves the way for efficient, scalable architectures in next-generation AI, storage, and edge environments.

The Chelsio offload model has been refined over multiple generations of silicon, enabling the T7 to run all prior-gen software (T4, T5, and T6) without modification. This software continuity ensures investment protection and seamless migration to faster Ethernet and PCIe speeds with future T7 silicon.

Industry Recognition

Chelsio recently sponsored an IDC Analyst Brief titled DPUs Enable Secure, Flexible, and Efficient Semiconductor Solutions in the Datacenter and at the Heavy Edge. The report highlights how DPUs, such as T7, are transforming data center architectures by offloading infrastructure workloads and enabling scalability for AI and storage over Ethernet.

“DPUs offer a compelling solution for organizations looking to support AI and storage workloads on Ethernet,” said Brandon Hoff, executive analyst, IDC. “The Chelsio T7 DPU offers high-performance offloads and congestion control based on open standards; capabilities that make it a flexible and scalable option for modern infrastructure needs from a company with a strong track record.“

Chelsio at FMS 2025

Chelsio will be exhibiting at the Future of Memory and Storage (FMS) 2025, taking place from August 5 to 7 in Santa Clara, CA. Visit Booth 851 for a video preview of the T7 architecture and its capabilities in high-performance storage, security, and AI networking.

Resources:

T7 and S7 Adapter Selector Guide

T7 DPU Product Brief

S7 SmartNIC Product Brief

DPUs Enable Secure, Flexible, and Efficient Semiconductor Solutions in the Datacenter and at the Heavy Edge (IDC Analyst Brief)

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter