Flash Memory Summit: Wolley Announces CXL Design and Integration Services

Based on in-house developed and PCI-SIG 5.0 certified CXL controller IP core, CXL Design and Integration Services Group focusing on ASIC and FPGA implementation for datacenter and AI/ML computational applications

This is a Press Release edited by StorageNewsletter.com on August 8, 2023 at 2:02 pmWolley Inc., a Silicon Valley high performance storage interface and controller company, announces its CXL Design and Integration Services Group focusing on the ASIC and FPGA implementation for datacenter and AI/ML computational applications.

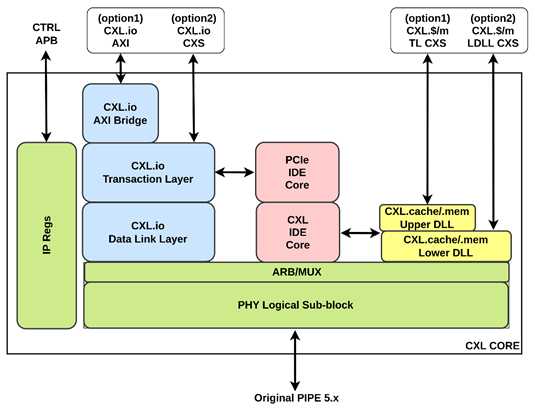

![]() Based on its in-house developed and PCI-SIG 5.0 certified CXL controller IP core, the CXL Design and Integration Services Group offers a one-stop and end-to-end CXL (Compute Express Link) design and integration services, from architecture design, spec-in, circuit design, verification, firmware, to RTL.

Based on its in-house developed and PCI-SIG 5.0 certified CXL controller IP core, the CXL Design and Integration Services Group offers a one-stop and end-to-end CXL (Compute Express Link) design and integration services, from architecture design, spec-in, circuit design, verification, firmware, to RTL.

CXL/PCIe Controller IP carries out CXL 3.0 specification

and is backward compatible to CXL 2.0 and 1.1.

Possessing high customizability and supportability, controller provides CXL solution.

By leveraging the end-to-end integration for CXL related ASIC or FPGA implementation, customers can focus on exploring new architecture and system-level innovations enabled by CXL’s capabilities. CXL allows customers to increase scalability, optimize data flow with switching and fabric capability, streamline peer-to-peer communications, and maximize resource sharing across multiple compute domains. This also allows customers to bring solutions to enterprise or multi-tenant server platforms.

To demo its design and integration expertise at FMS, the company will host a live demo of a 4-port CXL switch implemented on a Xilinx vu19p FPGA platform. This CXL switch will connect 2 hosts that are commercially available CXL 1.1 servers with a Wolley CXL 2.0 Multiple-Logic-Device (MLD) End-point device implemented on a Xilinx vu13p FPGA. To further demo its CXL IP technology at FMS, Wolley will present a paper, Making the Case for CXL Native Memory, to explore an idea that will expand the CXL benefits from HPC to low power mobile memory applications.

“Since 2019, our engineering team started the development of the CXL/PCIe IP from the ground up. The team has successfully obtained the PCI-SIG 5.0 certification earlier in 2023,” said Dr. Bernard Shung, president and founder.

The company has partnered with a tier-1 highspeed interface IP provider since 2022 in providing a total CXL/PCIe solutions. Wolley’s controller IP core supports up to CXL 3.0 and PCIe Gen6 x16, plus the IDE capability through a separate CXL/PCIe IDE IP. The controller IP has been validated on Xilinx UltraScale+ FPGA platform as well as on Xilinx Versal FPGA platform.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter