Flash Memory Summit: Phison PS8313 UFS 2.1 Controller

Brings to mobile performance CoXProcessor 2.0 technology from PCIe SSD.

This is a Press Release edited by StorageNewsletter.com on August 16, 2017 at 2:24 pmPhison Electronics Corp. announced the PS8313 UFS 2.1 controller at the Flash Memory Summit.

PS8313 UFS 2.1 controller demo

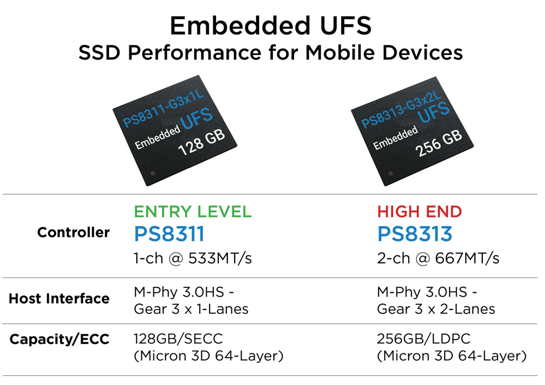

PS8313 is a performing two-lane chip targeting tier-1 flagship mobile chipsets and smartphones. Taking advantage of the latest generation of 3D TLCs, the solution addresses the increasing capacity and cost per density requirements from the fast-changing mobile market.

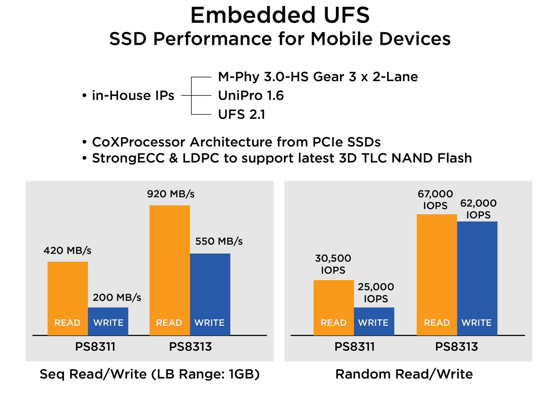

UFS, or Universal Flash Storage, is the high-speed interface standard aimed to replace eMMC in mobile phones and SD cards in memory card applications. The latest UFS 2.1 specification is equipped with increasing data rates and a differential-signaling serial interface with full-duplex operation. Currently, the mobile application processors are gearing up the two-lane UFS interface support at 1,200MB/s, three times the speed over its predecessor eMMC, and PS8313 will be a independent UFS controller to meet the impressive throughput requirement. The PS8313’s sequential and random R/W speeds on 3D NAND are topping 920/550MB/s and 67,000/62,000 IO/s, which are comparable to SATA SSDs, bringing a new experience to the ultimate smartphone users for gaming, high-resolution video and streaming applications.

PS8313 utilizes a 28nm process while the company’s in-house M-PHY, UniPro and UFS IPs gives a control over the solution for scalability. Equipped with a compact and low-power LDPC ECC engine designed for the latest 3D TLC, the controller effectively enhances memory endurance and reliability.

The design also removes the need for additional passive components in the UFS package, simplifying the BOM for the device manufacturers.

Supporting a maximum of eight NAND dice, PS8313 can enable up to 256GB of NAND storage into several form factors such as the UFS Card, discrete BGA, or UFS-based multichip packages with low-power DRAM (uMCPs) for different mobile applications.

PS8313 controller consists of following features:

-

UFS 2.1 compliant, high-speed gear 3, x2 lane throughput

-

CoXProcessor 2.0 architecture for NAND operation management, inherited from the company’s PCIe controllers

-

New architecture enables PS8313 lower system latency and higher random performance. In a 128GB UFS configuration, the measured performance is similar to a high-end client SATA SSD

-

In-house M-PHY 3.x (high-speed gear 3, x2 Lane), UniPro 1.6x and UFS 2.1 IPs passing various compliance and chipset validations

-

LDPC ECC with Adaptive Signal Processing, a 30% improvement in correction capability over a traditional LDPC engine

-

Maximum 3D TLC Sequential R/W – 920/550MB/s (*)

-

Maximum 3D TLC 4K Random R/W – 67,000/62,000 IO/s (*)

“Phison aims to support the tier-1 smartphone flagship models by introducing the UFS 2-lane PS8313 controller“, said K.S. Pua, CEO and co-founder, Phison. “For the best phones in the market, it will be exciting to see the powerful SSD-level performance on a small 11.5x13mm UFS BGA package. This is one of the most innovative solutions we are enabling with our partners’ 3D TLC NAND, contributing to an incredible application experience in the premium smartphone segment where the most competitive performance gets extra attention.“

(*) Raw performance without OS based on internal testing; performance may be lower depending upon host platform

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter