FMS 2025: UCIe Consortium Introduces 3.0 Specification With 64GT/s Performance and Enhanced Manageability

UCIe-S and UCIe-A to power next-gen multi-chip systems for evolving use cases, which demand higher bandwidth density, such as AI, by doubling data rate while maintaining low power.

This is a Press Release edited by StorageNewsletter.com on August 7, 2025 at 2:00 pmSummary:

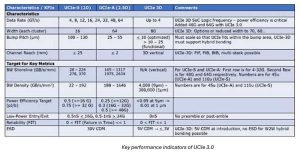

- UCIe 3.0 specification delivers 48/64GT/s speeds for UCIe-S and UCIe-A to power next-gen multi-chip systems for evolving use cases, which demand higher bandwidth density, such as AI, by doubling the data rate while maintaining low power.

- New features boost power efficiency, enhance manageability, and expand design flexibility for scalable SiP architectures.

- Designed to accelerate high-performance, modular semiconductor development across a rapidly growing chiplet ecosystem.

Universal Chiplet Interconnect Express (UCIe) Consortium, the open standard for interconnects between chiplets within a package, announced the release of the UCIe 3.0 specification, marking the next stage in the evolution of its open chiplet standard.

The new specification delivers significant performance enhancements, most notably support for 48 and 64GT/s data rates, alongside incremental architectural updates to meet growing industry demand for high-speed, interoperable chiplet solutions.

The UCIe 3.0 specification also introduces enhancements such as runtime recalibration for improved power efficiency and extended sideband reach that supports more flexible multi-chip configurations. Additional manageability features like early firmware download and priority sideband packets increase system responsiveness and reliability. The specification’s optional manageability features give companies the flexibility to implement only what they need, enabling broad adoption while allowing design customization without unnecessary silicon.

Together, these advancements reflect the Consortium’s commitment to driving innovation in the chiplet ecosystem by improving bandwidth density, power efficiency, and system-level manageability, key enablers for scalable multi-chip System-in-Package (SiP) designs. As a result, the 3.0 specification enables greater scalability, flexibility, and interoperability to accelerate innovation in modular semiconductor design.

“UCIe 3.0 represents a critical step forward for the chiplet industry, delivering the speed, efficiency, and manageability needed to scale multi-chip designs,” said Cheolmin Park, president, UCIe Consortiumn and corporate VP, Samsung Electro-Mechanics. “With increased data rates and extended manageability capabilities, the next generation of UCIe technology will empower developers to build more flexible, interoperable, and high-performance SiP solutions as we all work together to build a truly open and interoperable chiplet ecosystem.”

Click to enlarge

UCIe 3.0 Specification Highlights:

- Support for 48 and 64GT/s data rates, doubling the bandwidth of UCIe 2.0 (32GT/s) to meet high-performance chiplet demands

- Runtime recalibration enhancements enable power-efficient link tuning during operation by reusing initialization states

- Extended sideband channel reaching up to 100mm supports more flexible SiP topologies

- Support for continuous transmission protocols through mappings, enabling uninterrupted data flow in Raw Mode for new applications such as connectivity between SoC and DSP chiplets

- Early firmware download standardization using Management Transport Protocol (MTP) for streamlined initialization

- Priority sideband packets allow deterministic, low-latency signaling for time-sensitive system events

- Fast throttle and emergency shutdown mechanisms provide immediate system-wide notifications via open-drain I/O

- Fully backward compatible with all previous UCIe specifications for seamless integration and adoption

Learn more about the UCIe 3.0 Specification at Future of Memory and Storage (FMS)

Swadesh Choudhary, UCIe Consortium, will introduce new features included in the UCIe 3.0 Specification at FMS: the Future of Memory and Storage 2025 on Thursday, August 7, 2025, from 8:30 – 9:35 am PT in the Santa Clara Convention Center, CA. The UCIe Consortium will also host a kiosk in the FMS Open Standards Pavilion (Booth 725) on the exhibit show floor from August 5-7.

Resources:

UCIe 3.0 Specification is available to the public by request

UCIe 3.0 White Paper (PDF)

UCIe Consortium member statement of support (PDF)

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter