Cadence Introduces Industry-First LPDDR6/5X 14.4Gb/s Memory IP

To power next-gen AI infrastructure, integrated subsystem optimized for customer applications including chiplets

This is a Press Release edited by StorageNewsletter.com on July 24, 2025 at 2:00 pmCadence Design Systems, Inc. announced a first LPDDR6/5X memory IP system solution optimized to operate at 14.4Gb/s, up to 50% faster than the previous-gen of LPDDR DRAM.

The new Cadence LPDDR6/5X memory IP system solution is a key enabler for scaling up the AI infrastructure to accommodate the memory bandwidth and capacity demands of next-generation AI LLMs, agentic AI and other compute-heavy workloads for various verticals. Multiple engagements are currently underway with leading AI, HPC and data center customers.

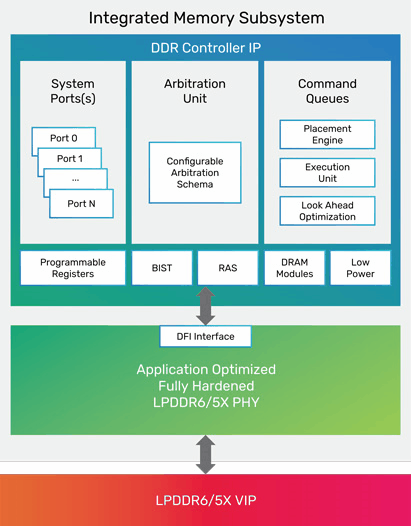

The Cadence IP for the JEDEC LPDDR6/5X standard consists of an advanced PHY architecture and a high-performance controller designed to maximize power, performance and area (PPA) while supporting both LPDDR6 and LPDDR5X DRAM protocols for optimal flexibility. The solution supports native integration into traditional monolithic SoCs as well as multi-die system architectures by leveraging the company’s chiplet framework, enabling heterogeneous chiplet integration. The chiplet framework, including the previous LPDDR generation, was successfully taped out in 2024.

“The evolution of data centers from HPC compute virtualization to AI training and inference at scale has driven a massive buildout of AI infrastructure, and designing for efficient data movement via memory interfaces has never been more crucial. LPDDR6 has emerged as a key enabler of accelerated compute, providing the speed, bandwidth, power profile and capacity needed to efficiently perform AI inference,” said Boyd Phelps, SVP and GM, silicon solutions group, Cadence. “With this tapeout, Cadence is continuing our track record of memory IP leadership by offering an industry-first LPDDR6 implementation delivered as an integrated subsystem optimized for customer applications.”

The complete PHY and controller memory system boasts a new high-performance, scalable and adaptable architecture based on the company’s proven and highly successful DDR5 12.8Gb/s, LPDDR5X 10.7Gb/s and GDDR7-36G product lines. This 1st offering in Cadence’s new LPDDR6 IP product line supports the LPDDR6 and LPDDR5X standards, including LPDDR5X CAMM2.

Suitable for the AI, mobile, consumer, enterprise HPC and cloud data center markets, the advanced LPDDR6/5X memory IP system solution allows maximum flexibility for end products with a range of performance, capacity and cost targets – ensuring long production runs. The LPDDR6/5X PHY is customizable for different package and system topologies and available as a drop-in hardened macro. This ensures fast and reliable integration, translating into rapid time to market.

The Cadence LPDDR6/5X controller includes a full set of industry-standard and advanced features for memory interfaces, such as support for the Arm AMBA AXI bus. The memory controller is provided as a soft RTL macro for maximum flexibility in features, power, area and performance.

The firm’s LPDDR6 solution includes the LPDDR6 Memory Model, which enables engineers to perform comprehensive verification and ensure that SoC designs are compatible with the latest JEDEC interface standard, accelerating their adoption of this new technology with confidence. The LPDDR6 Memory Model includes a complete set of protocol checks, functional coverage and a verification plan.

Available for customer engagements, the new LPDDR6/5X IP is the latest addition to the company’s family of memory IP system solutions, which also includes DDR, GDDR and HBM. Cadence Memory IP is designed with the firm’s analog/mixed-signal design tools. When combined with the company’s UCIe -based chiplet framework, the new LPDDR6/5X IP and Cadence’s other memory and interface IP deliver an optimized solution that enables rapid chiplet realization.

Resource:

LPDDR PHY and Controller webpage

Family of High-Speed On-Chip Memory Interface IP

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter