Astera Labs Leo Memory Connectivity Platform Enables Data Center Servers with Performance for Memory Intensive Workloads

CXL memory controller increases memory bandwidth by 50% and reduces latency by 25% with Intel server platforms.

This is a Press Release edited by StorageNewsletter.com on September 28, 2023 at 2:02 pmAstera Labs, Inc. announced that its Leo Memory Connectivity Platform enables data center servers with performance for memory intensive workloads.

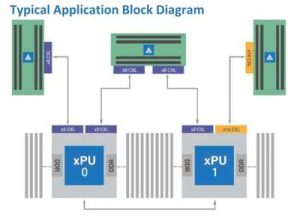

Leo is the 1st Compute Express Link (CXL) memory controller that increases total server memory bandwidth by 50% while also decreasing latency by 25% when integrated with the forthcoming 5th Gen Xeon Scalable Processor. Through new hardware-based interleaving of CXL-attached and CPU native memory, Astera Labs and Intel Corp. eliminate any application-level software changes to augment server memory resources via CXL. Existing applications can ‘plug-and-play’ to take advantage of the highest possible memory bandwidth and capacity in the system.

“The growth of computing cores and performance has historically outpaced memory throughput advancements, resulting in degraded server performance efficiency over time,” said Sanjay Gajendra, COO, Astera Labs. “This performance scaling challenge has led to the infamous ‘memory wall,’ and thanks to our collaboration with Intel, our Leo Memory Connectivity Platform breaks through this barrier by delivering on the promise of PCIe 5.0 and CXL memory.”

Data center infrastructure scaling limitations due to the memory wall are none more evident than in AI servers where memory bandwidth and capacity bottlenecks result in inefficient processor utilization. The CXL innovations delivered by the company and Intel directly address these bottlenecks and lay the foundation for cloud, hybrid-cloud and enterprise data centers to maximize accelerated computing performance.

Extending leadership of PCIe 5.0 and CXL 2.0 solutions

The company has a history of delivering industry-first solutions that are critical to advancing the PCIe and CXL ecosystems. In addition to memory performance advancements with Leo, the firm is also driving interoperability leadership with its Aries PCIe 5.0 / CXL 2.0 Smart Retimers on Intel server platforms. As the most widely deployed and proven PCIe/CXL retimer family in the industry, Aries features a low-latency CXL mode that complements Leo to form a robust CXL memory connectivity solution.

“We applaud Astera Labs for their contributions to the CXL ecosystem and are delighted to extend our ongoing collaboration. We believe Memory Connectivity Platforms containing innovations from companies like Astera Labs will help deliver enhanced performance on next generation Intel Xeon processors, and accelerate a myriad of memory intensive workloads,” said Zane Ball, corporate VP and GM, data center platform engineering and architecture group, Intel.

Resources:

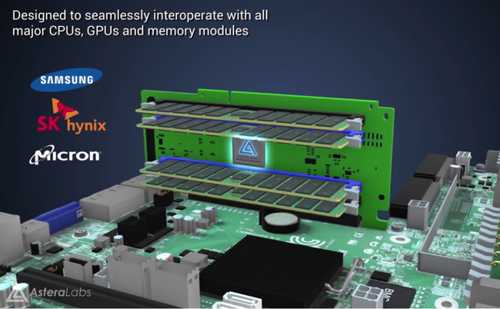

Astera Labs delivers Leo CXL Memory Connectivity Platform

Leo CXL Memory Connectivity Platform

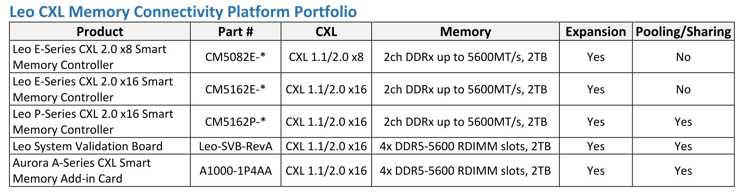

Leo E-Series CXL Smart Memory Controller supporting memory expansion

Leo P-Series CXL Smart Memory Controller supporting memory expansion, pooling, and sharing

Aurora A-Series Smart Memory Hardware Solutions in add-in-card form factor supporting memory expansion, pooling and sharing

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter