Renesas Circuit Technologies for 22nm Embedded STT-MRAM

With faster RW performance for MCUs in IoT applications

This is a Press Release edited by StorageNewsletter.com on June 23, 2022 at 3:02 pmRenesas Electronics Corp. developed circuit technologies for an embedded STT-MRAM (hereinafter MRAM) test chip with fast RW operations fabricated using a 22nm process.

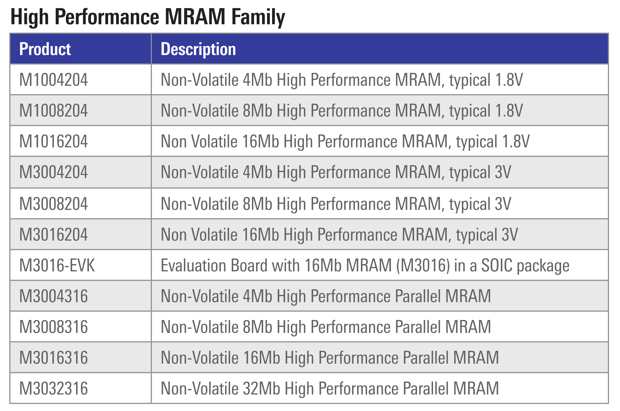

The test chip includes a 32Mb embedded MRAM memory cell array and achieves 5.9ns random read access at a maximum junction temperature of 150°C, and a write throughput of 5.8MB/s.

The company presented these achievements on June 16 at the 2022 IEEE Symposium on VLSI Technology and Circuits, held between June 12 and 17 in Hawaii.

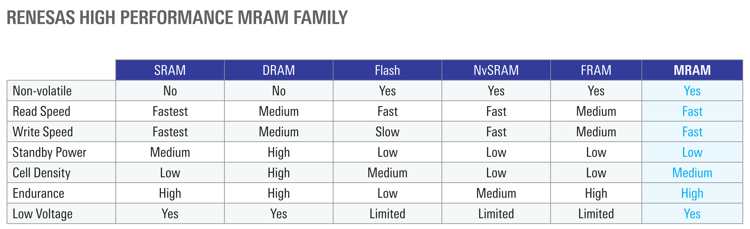

As the advances of IoT and AI technologies continue, MCUs used in endpoint devices are expected to deliver higher performance, and therefore need to be fabricated with finer process nodes. MRAM fabricated in BEOL (1) is advantageous compared to flash memory fabricated in FEOL (2) for sub-22nm processes because it is compatible with existing CMOS logic process technology and requires fewer additional mask layers. However, MRAM has a smaller read margin than flash memory, which degrades read speed. A large gap between the CPU operating frequency and the read frequency of the non-volatile memory is also a challenge since it can degrade MCU performance.

MRAM can also achieve shorter write time than flash memory because it requires no erase operation before write operation. However, further speed improvements are needed to shorten system downtime for over-the-air (OTA) updates required for endpoint devices and reduce costs for end product manufacturers in writing control codes for MCUs.

To address these challenges and respond to market demand for higher MCU performance, the company has developed the following new circuit technologies to achieve faster RW operation in MRAM.

1. Fast read technology employing high-precision sense amplifier circuit

MRAM uses memory cells including magnetic tunnel junction (MTJ) devices in which high and low-resistance states correspond to data values of 1 and 0 respectively to store information. A differential sense amplifier distinguishes between the two states by reading the voltage difference in discharge speed between the memory cell current and reference current. However, since the memory cell current difference between the 1 and 0 states is smaller for MRAM than for flash memory, the voltage difference read by the sense amplifier is smaller. Even if the discharge time is extended to wider voltage differences between the differential input nodes of the sense amplifier, both of the input nodes are susceptible to being completely discharged before securing a necessary voltage difference. This problem is particularly acute at high temperatures.

To resolve this issue, the firm introduced a new technology utilizing capacitive coupling to boost the voltage level of the differential input nodes, allowing the differential amplifier to sense a voltage difference even when the memory cell current difference is small, achieving high-precision and fast read operation.

2. Fast write technology with simultaneous write bit number optimization and shortened mode transition time

Following the high-speed write technologies for embedded STT-MRAM announced in December 2021, this technology achieves even higher speed by shortening the mode transition time during write operation.

This technology divides up the areas to which write voltage is applied and, by inputting the write address before the write voltage setup, it selectively applies voltage only to the necessary area. This method reduces the parasitic capacitive load on the area where the voltage is applied during the write operation, reducing the voltage setup time. As a result, the mode transition time to write operation is reduced by approximately 30%, speeding up write operation.

The company continues to develop technologies aimed at the application of embedded MRAM technology in MCU products. These technologies have the potential to dramatically boost memory access speed, which is currently a challenge with MRAM, to exceed 100MHz, enabling performance MCUs with embedded MRAM. Faster write speed will contribute to more efficient code writing to endpoint devices. The firm is committed to further increasing capacity, speed, and power efficiency for MCUs to accommodate new applications.

(1) BEOL stands for ‘back end of line’ and designates the latter portion of semiconductor fabrication from deposition of metal interconnect layers to completion.

(2) FEOL stands for ‘front end of line’ and designates the first portion of semiconductor fabrication where devices are patterned in the substrate and before the deposition of metal interconnect layers.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter