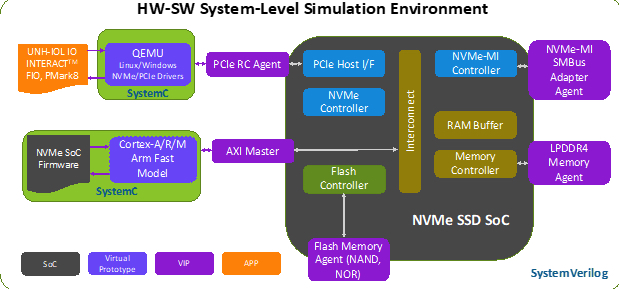

Avery Design QEMU Virtual Host to SystemVerilog PCIe VIP HW-SW Co-Simulation Solution

For pre-silicon system-level simulation of NVMe SSD and PCIe designs

This is a Press Release edited by StorageNewsletter.com on November 18, 2020 at 2:09 pmAvery Design Systems announced the pre-silicon system simulation solution of NVMe SSD and PCIe designs using QEMU virtual host to SystemVerilog PCIe VIP co-simulation, thus enabling the functional validation of complete NVMe and PCIe hardware-software SoC designs using standard conformance and performance benchmarking software applications running in Linux and Windows environments.

“Early HW-SW integration and verification accelerates the development schedule and reduces bug fix times and iterations dramatically,” said Chris Browy, VP, sales and marketing. “We are pleased to expand the capability of our industry leading, SystemVerilog-based PCIe and NVMe VIP to support virtual host prototyping and address the needs of both hardware and software design teams.“

Co-simulating the actual SoC RTL with a QEMU open software VM emulator environment running any number of Linux or Windows OS builds allows software engineers to natively develop and build any of their custom firmware, drivers, and applications and run them unaltered and debug software issues using standard debuggers (GDB and KGDB) as part of a validation process of the SoC operation vs. the cycle accurate and detailed SystemVerilog RTL representation of the hardware. In a complementary manner, HW engineers can evaluate how their SoC performs through executing PCI BIOS and expansion ROM code, OS boot, and custom driver initialization sequences in addition to running real application workloads and utilizing the PCIe and NVMe VIP protocol aware debugging features to investigate any hardware related issues.

Hardware or software design iterations can be turned around and evaluated rapidly and enable a smoother transition from simulation to FPGA prototyping wherein the SoC design can go through stress and interoperability testing.

System bring-up and validation using standards-based conformance and interoperability testing is now feasible across a wide range of designs – NVMe SSDs, smart NICs, PCIe switches and retimers, and a myriad of other PCIe endpoint-based peripherals.

Examples include:

-

NVMe SSD validation requires executing the UNH-IOL Interact test software in addition to other performance benchmarking applications such as FIO, PMark8, and CrystalDiskMark.

-

PCIe compliance requires passing the PCI-SIG PCIeCV and interoperability tests at a PCI-SIG Compliance Workshop.

“Supporting IOL Interact in a QEMU/PCIE VIP system-level co-simulation platform for in-house testing at the pre-silicon level gives IOL INTERACT users great confidence that their products will meet the NVMe integrator’s list requirements when submitted for testing,” said David Woolf, senior Engineer, datacenter technologies, UNH-IOL (University of New Hampshire InterOperability Laboratory). “We are pleased to collaborate with Avery to have this solution supported for our latest IOL Interact release deploying the UNH-IOL NVMe Conformance and UNH-IOL NVMe Interoperability test plans.“

Read also:

Flash Memory Summit: NVMe 1.3 and NVMe-MI Verification IP Updates by Avery Design Systems

Support for NVMe-Management Interface (NVMe-MI) over PCIe 4.0 or SMBus 3.0.

August 15, 2017 | Press Release

Avery Design Systems Scale-Out With NVMe over Fabrics Verification Solutions

Verification solution for NVMe core and subsystem design

August 19, 2016 | Press Release

NVMe over Fabrics 1.0 and 1.2.1 Extensions Available From Avery Design Systems

Verification solutions

August 16, 2016 | Press Release

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter