Toshiba Expands Line-up of e-MMC Version 5.1 Embedded NAND Flash Memory Modules

16GB to 128GB, support command queuing, secure write protection features

This is a Press Release edited by StorageNewsletter.com on April 2, 2015 at 3:16 pmToshiba America Electronic Components, Inc. (TAEC) announced its JEDEC e-MMC Version 5.1 compliant embedded NAND flash memory products.

Featuring support for command queuing and secure write protection, the modules integrate NAND chips fabricated with Toshiba’s 15nm second generation process technology and are compliant with the latest e-MMC (1) standard. The products are designed for application in a range of digital consumer products, including smartphones, tablets and wearable devices.

In October 2014, Toshiba launched the industry’s first (2) e-MMC products supporting all mandatory features of JEDEC e-MMC Version 5.1, which was officially issued by JEDEC on February 24, 2015. The additions to the line-up support two optional features of e-MMC Version 5.1: command queuing and secure write protection.

The command queuing feature enables users to store multiple tasks in a queue, which are then performed in order of the user’s preference to enhance performance. It improves the random read performance speed by up to 30% (3) when compared to existing Toshiba products that do not have command queuing. This feature improves the user experience, allowing the simultaneous execution of multiple applications at the same time – a typical scenario for users of mobile devices such as smartphones and tablets.

The secure write protection feature expands the conventional write protect feature and protects important data stored in assigned, secure areas from being overwritten or erased by unauthenticated users.

“Toshiba has been supporting e-MMC Version 5.1 since it first came out last year for a variety of applications,” noted Scott Beekman, director, managed NAND memory products, TAEC. “The addition of these optional Version 5.1 features further enhances our product offering, and points to Toshiba’s continued leadership role in NAND flash and embedded memory solutions.”

Demand continues to grow for large density NAND flash memory chips that support high resolution video and deliver enhanced storage. This is particularly true in the area of embedded memories with a controller function, which minimize development requirements and ease integration into system designs. Toshiba is meeting this demand by reinforcing its line-up of high density memory products.

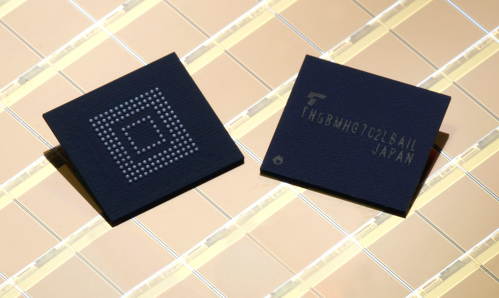

Toshiba’s line-up of single-package embedded NAND flash memories includes densities from 16 to 128GB. Each device integrates a controller to manage basic control functions for NAND applications. Sample shipments of the 16 and 64GB products begin today, with additional densities (including 32 and 128GB) to follow.

| Product Name | Capacity | Category | Package | Mass Production |

|---|---|---|---|---|

| THGBMHG7C2LBAIL | 16GB |

Supreme

|

11.5x13x0.8mm | 2Q, 2015 (Apr.-Jun.) |

| THGBMHG8C4LBAIR | 32GB | 11.5x13x1.0 mm | 2Q, 2015 (Apr.-Jun.) | |

| THGBMHG9C8LBAIG | 64GB | 11.5x13x1.2 mm | 2Q, 2015 (Apr.-Jun.) | |

| THGBMHT0C8LBAIG | 128GB | 11.5x13x1.2 mm | 2Q, 2015 (Apr.-Jun.) |

*In Toshiba e-MMC categories, ‘Supreme’ represents products suited to high-end class applications.

Key features

The JEDECe-MMC Version 5.1 compliant interface handles essential functions, including writing block management, error correction and driver software. It simplifies system development, allowing manufacturers to minimize development costs and speed up time to market for new and upgraded products. Additionally, new features (4) standardized in JEDECe-MMC Version 5.1, such as BKOPS control, Cache Barrier, Cache Flushing Report and Large RPMB Write, are applied to the new products to enhance usability.

The random read performance can be improved by up to 30% (max.) (3) by applying the ‘command queuing feature,’ one of the new optional features of JEDECe-MMC Version 5.1.

Embedded in a system, the 128GB products can record up to 16.3 hours of full spec high definition video and 39.7 hours of standard definition video (5).

| Interface |

JEDEC e-MMC V5. 1 standard |

|---|---|

| Capacity |

16, 32, 64, 128GB

|

| Power Supply Voltage |

2.7-3.6V (Memory core) |

| Bus Width |

x1 , x4 , x8

|

| Temperature Range |

-25°C to +85°C

|

| Package |

153Ball FBGA

1.5mm x 13.0mm |

Notes

(1) e-MMC is a product category for a class of embedded memory products built to the JEDEC e-MMC Standard specification and is a trademark of the JEDEC Solid State Technology Association. The latest JEDEC e-MMC Version 5.1 specification was officially issued by JEDEC on February 24, 2015.

(2) As of October 2, 2014. Toshiba survey.

(3) Toshiba survey.

(4) ‘BKOPS control’ is a function where the host allows the device to perform background operation when the device is idle. ‘Cache Barrier’ is a function that controls when cache data is written to the memory chip. ‘Cache Flushing Report’ is a function that informs the host if the device’s flushing policy is FIFO (First In First Out) or not. ‘Large RPMB write’ is a function that enhances the data size that can be written to the RPMB area to 8KB.

(5) HD and SD are calculated at average bit rates of 17Mb/ps and 7Mb/s, respectively.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter